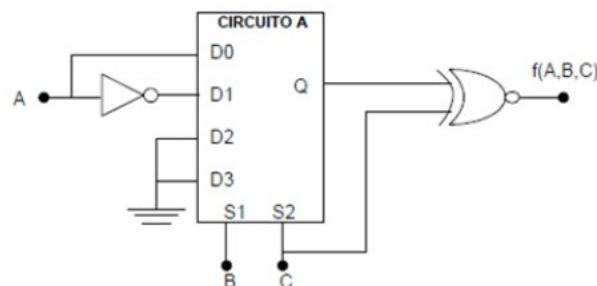

En el circuito de la figura, el circuito A es un multiplexor en el que  $S_1$  es la señal de selección de más peso. Se pide:

- Obtenga la tabla de verdad de la función  $f$ .

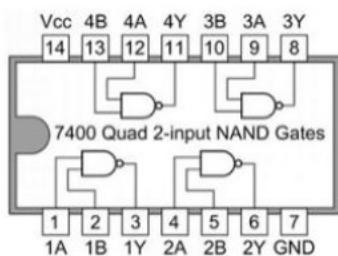

- El circuito integrado 7400 tiene cuatro puertas NAND de dos entradas (ver esquema adjunto). Tratando de utilizar el menor número de circuitos posible, ¿cuántos circuitos 7400 serían precisos para implementar la función  $f$ ?

- Realice la función  $f$  con un multiplexor de tres líneas de selección y los inversores que considere necesario (en número mínimo).

- Realice la función  $f$  con un decodificador de nivel activo bajo de tres entradas y una puerta AND.

Circuito integrado 7400

Circuito A - Multiplexor

- En primer lugar, analizamos el MUX. Sus entradas de selección son:

$$S_1 = B(\text{MSB})$$

$$S_2 = C(\text{LSB})$$

La salida Q del MUX selecciona una de las entradas de datos  $D_i$  según el valor de BC:

$$BC = 00 \Rightarrow Q = D_0 = A$$

$$BC = 01 \Rightarrow Q = D_1 = \bar{A}$$

$$BC = 10 \Rightarrow Q = D_2 = 0(\text{tierra})$$

$$BC = 11 \Rightarrow Q = D_3 = 0(\text{tierra})$$

La tabla de verdad será entonces:

| <b>A</b> | <b>B</b> | <b>C</b> | <b>Q</b>           | $f = \overline{Q} \oplus C$ |

|----------|----------|----------|--------------------|-----------------------------|

| 0        | 0        | 0        | A=0                | 1                           |

| 0        | 0        | 1        | $\overline{A} = 1$ | 1                           |

| 0        | 1        | 0        | 0                  | 1                           |

| 0        | 1        | 1        | 0                  | 0                           |

| 1        | 0        | 0        | A=1                | 0                           |

| 1        | 0        | 1        | $\overline{A} = 0$ | 0                           |

| 1        | 1        | 0        | 0                  | 1                           |

| 1        | 1        | 1        | 0                  | 0                           |

b. La función lógica obtenida expresada en 1<sup>a</sup> forma canónica (minterms) es:

$$f(A, B, C) = \sum_i (0, 1, 2, 6)$$

Utilizando mapas de Karnaugh para simplificar:

|   |   | BC | 00 | 01 | 11 | 10 |

|---|---|----|----|----|----|----|

|   |   | A  | 0  | 1  | 1  |    |

| 0 | 0 |    |    |    |    |    |

|   | 1 |    |    |    |    |    |

$$f(A, B, C) = \overline{A} \cdot \overline{B} + B \cdot \overline{C}$$

Utilizando las Leyes de De Morgan para implementarla con puertas NAND:

$$F = (A, B, C) = \overline{\overline{\overline{A} \cdot \overline{B}} + \overline{B \cdot \overline{C}}} = \overline{\overline{\overline{A} \cdot \overline{B}} \cdot \overline{B \cdot \overline{C}}}$$

- 1 puerta NAND para conseguir el inverso de A

- 1 puerta NAND para conseguir el inverso de B

- 1 puerta NAND para conseguir el inverso de C

- 1 puerta NAND para el producto  $\overline{A} \cdot \overline{B}$

- 1 puerta NAND para el producto  $B \cdot \overline{C}$

- 1 puerta NAND para el producto final

En total necesitamos entonces seis puertas NAND. Como el integrado 7400 tiene cuatro puertas NAND, necesitaremos dos integrados 7400.

- c. Para un multiplexor de 8 entradas ( $S_2S_1S_0 = ABC$ ), las entradas de datos  $D_i$  simplemente se conectan al valor de la función para ese minitérmino basándonos en la tabla de verdad obtenida en el apartado a:

- Conectamos a  $V_{cc}$  (1):  $D_0, D_1, D_2, D_6$

- Conectamos a GND (0):  $D_3, D_4, D_5, D_7$

| ABC | f | MUX                            |

|-----|---|--------------------------------|

| 000 | 1 | $D_0 \rightarrow V_{cc}(5V/1)$ |

| 001 | 1 | $D_1 \rightarrow V_{cc}$       |

| 010 | 1 | $D_2 \rightarrow V_{cc}$       |

| 011 | 0 | $D_3 \rightarrow GND(0V/0)$    |

| 100 | 0 | $D_4 \rightarrow GND$          |

| 101 | 0 | $D_5 \rightarrow GND$          |

| 110 | 1 | $D_6 \rightarrow V_{cc}$       |

| 111 | 0 | $D_7 \rightarrow GND$          |

- Conectamos la señal A a  $S_2$ , B a  $S_1$  y C a  $S_0$ .

- Las patillas  $D_0, D_1, D_2$  y  $D_6$  se puentean juntas y se conectan a nivel alto. Las demás se puentean y se llevan a masa (0).

- Como tenemos un MUX de 8 entradas para una función de 3 variables, no necesitamos inversores adicionales, ya que todas las combinaciones posibles de A, B y C están cubiertas directamente por los canales del multiplexor.

- d. Un decodificador de nivel activo bajo pone a 0 la salida correspondiente al número de entrada. Para obtener la función, debemos identificar en qué momento la función debe ser 0. Utilizando maxterms, las salidas 0 son 3, 4, 5 y 7.

En lógica de activo bajo, las salidas del decodificador son  $\bar{m}_i$ . Si usamos una puerta AND conectada a las salidas 3, 4, 5 y 7 tenemos:

$$f = \bar{m}_3 \cdot \bar{m}_4 \cdot \bar{m}_5 \cdot \bar{m}_7 = \overline{m_3 + m_4 + m_5 + m_7}$$

Esta función produce un 0 si cualquiera de las salidas se activa, que es exactamente lo que buscábamos.

---